# Single-phase metering chip MKE101R

## users manual

Rev 1.0

**Version Update Notice**

| version number | Modification time | revise content |

|----------------|-------------------|----------------|

| Rev 1.0        | 2025-02-13        | First release  |

## catalogue

|                                                                        |    |

|------------------------------------------------------------------------|----|

| 1 Chip Introduction .....                                              | 6  |

| 1.1 Chip Characteristics .....                                         | 6  |

| 1.2 Function Overview .....                                            | 7  |

| 1.3 Function Block Diagram .....                                       | 8  |

| 1.4 Pin Definitions .....                                              | 9  |

| 1.5 Typical Applications .....                                         | 11 |

| 1.5.1 State Grid Single-Phase 20 Version .....                         | 11 |

| 2 System Functions .....                                               | 13 |

| 2.1 Power Monitoring .....                                             | 13 |

| 2.2 System Reset .....                                                 | 13 |

| 2.3 Module Conversion .....                                            | 14 |

| 2.4 Active Power .....                                                 | 14 |

| 2.5 Reactive Power .....                                               | 15 |

| 2.6 Effective Value .....                                              | 15 |

| 2.7 Energy Calculation .....                                           | 16 |

| 2.8 Channel Switching .....                                            | 17 |

| 2.9 Frequency Measurement .....                                        | 17 |

| 2.10 Start-up of the Submerged Motor .....                             | 17 |

| 2.11 Event Detection .....                                             | 18 |

| 2.12 Interruption .....                                                | 18 |

| 2.13 Waveform Buffer .....                                             | 19 |

| 2.13.1 Characteristics of Waveform Buffer .....                        | 20 |

| 2.13.2 Waveform Buffering Method .....                                 | 20 |

| 2.13.3 Cache Address Mapping .....                                     | 23 |

| 2.13.4 Cache and Read Commands .....                                   | 25 |

| 2.13.5 Waveform Buffer Application Description .....                   | 28 |

| 2.14 Checksum and CRC (Cyclic Redundancy Check) .....                  | 29 |

| 2.14.1 Scope of Validation .....                                       | 29 |

| 2.14.2 Checksum .....                                                  | 32 |

| 2.14.3 CRC Verification Method .....                                   | 32 |

| 2.14.4 Switching Between Checksum and CRC16 Verification Methods ..... | 33 |

| 2.15 Register .....                                                    | 33 |

| 2.15.1 Register List .....                                             | 33 |

| 2.15.2 Calibration Parameter Registers .....                           | 43 |

| 2.1 5.3 Measurement Parameter Registers .....                          | 68 |

| 2.1 5.4 Interrupt Register .....                                       | 78 |

| 2.1 5.5 System Status Registers .....                                  | 81 |

| 2.1 5.6 Extended Registers .....                                       | 82 |

| 2.1 5.7 Special Orders .....                                           | 96 |

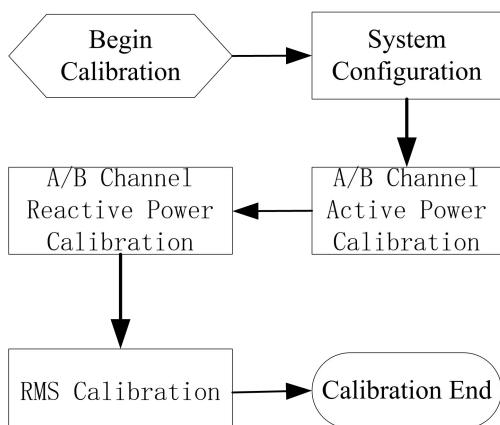

| 3 Calibration Method .....                                             | 99 |

| 3.1 Overview .....                                                     | 99 |

| 3.2 Calibration Process and Parameter Calculation .....                | 99 |

|                                                          |     |

|----------------------------------------------------------|-----|

| 3.2.1 Calibration Process .....                          | 99  |

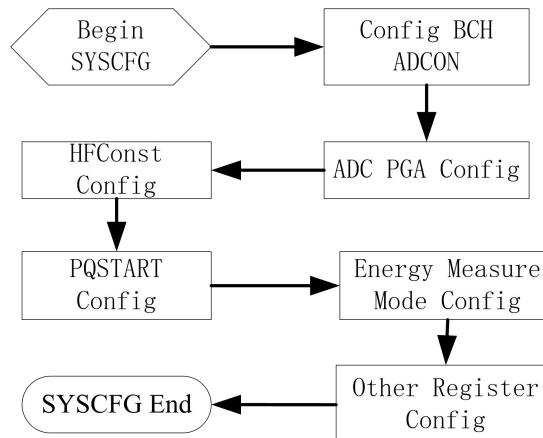

| 3.2.2 Parameter Settings .....                           | 100 |

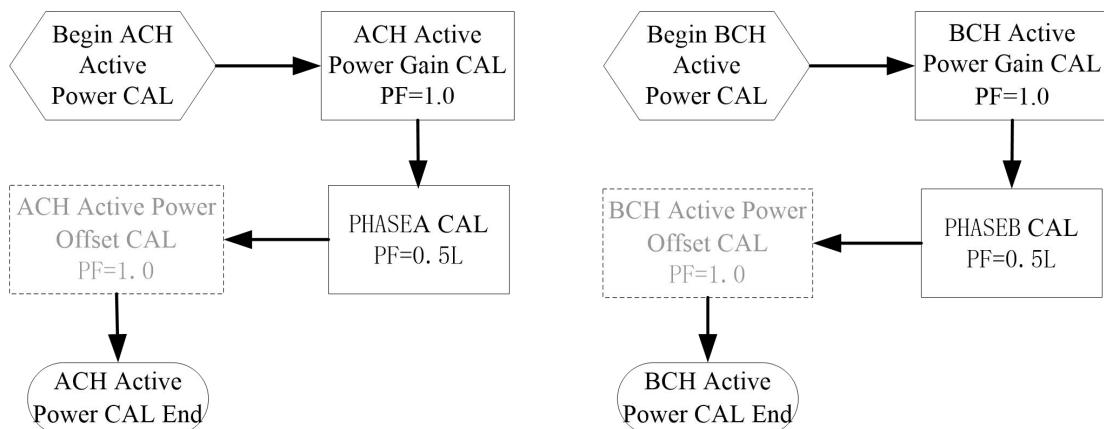

| 3.2.3 Active Power Correction .....                      | 100 |

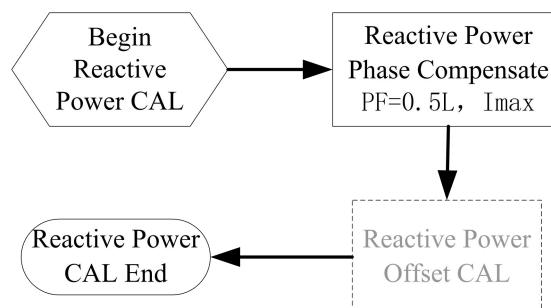

| 3.2.4 Reactive Power Correction .....                    | 101 |

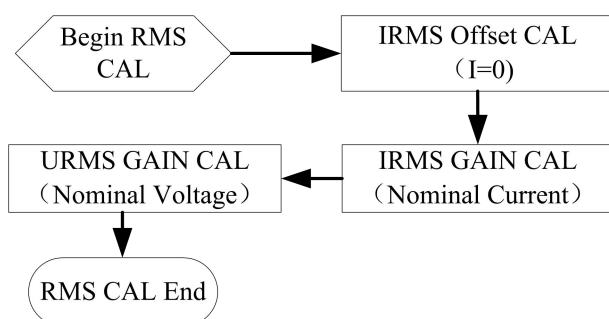

| 3.2.5 Valid Value Correction .....                       | 102 |

| 3.2.4 Examples .....                                     | 103 |

| 4 DC Application Description .....                       | 105 |

| 4.1 Overview .....                                       | 105 |

| 4.2 Basic Parameters .....                               | 105 |

| 4.3 DC OFFSET Correction .....                           | 105 |

| 4.3.1 Register Configuration .....                       | 105 |

| 4.3.2 Calculate the average of effective values .....    | 105 |

| 4.3.3 DC OFFSET Correction .....                         | 105 |

| 4.4 Effective Value OFFSET Correction .....              | 106 |

| 4.5 Conversion Coefficient .....                         | 106 |

| 4.6 Power Gain Correction .....                          | 107 |

| 4.7 Active Offset Correction .....                       | 107 |

| 4.7.1 Power Method Correction .....                      | 107 |

| 4.7.2 Error Method Correction .....                      | 107 |

| 5 Communication Interface .....                          | 109 |

| 5.2 UART Interface .....                                 | 109 |

| 5.2.1 Description of UART Interface Signals .....        | 109 |

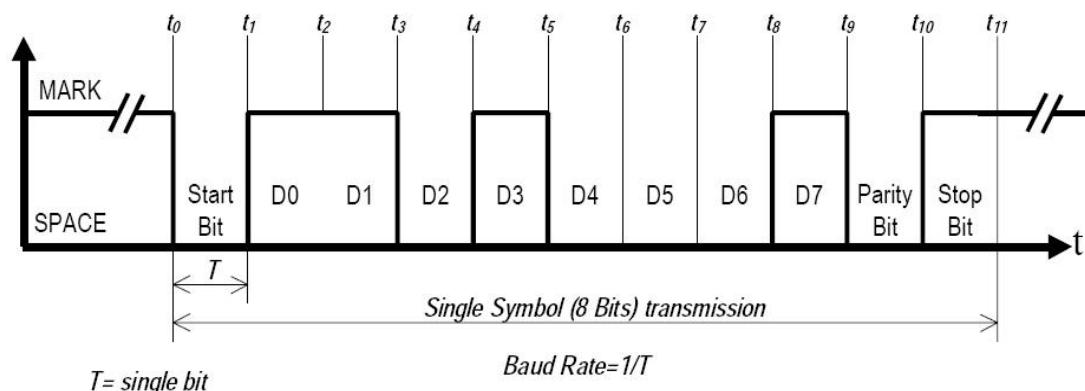

| 5.2.2 UART Data Byte Format .....                        | 109 |

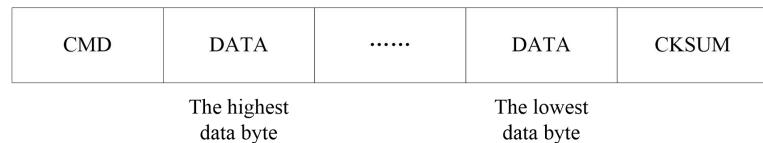

| 5.2.3 UART Frame Format .....                            | 109 |

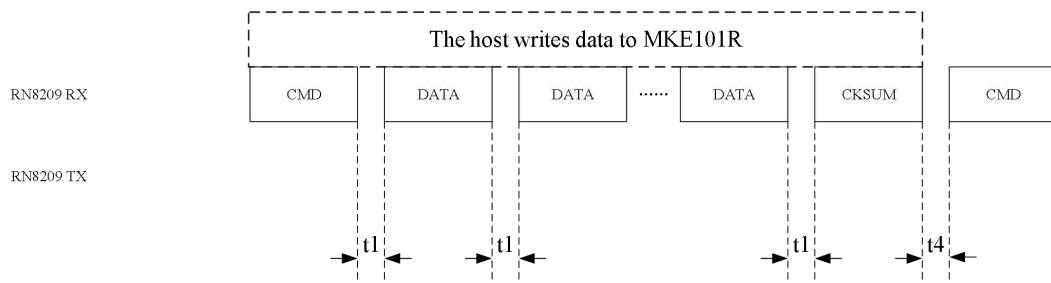

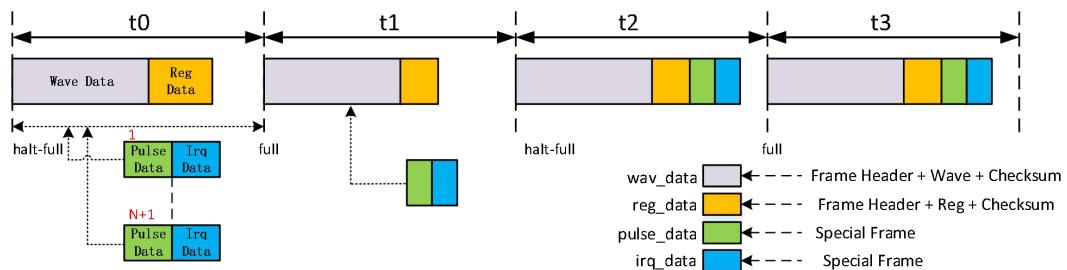

| 5.2.4 UART Write Operation .....                         | 111 |

| 5.2.5 UART Read Operation .....                          | 111 |

| 5.2.6 Reliability Design of UART Interface .....         | 112 |

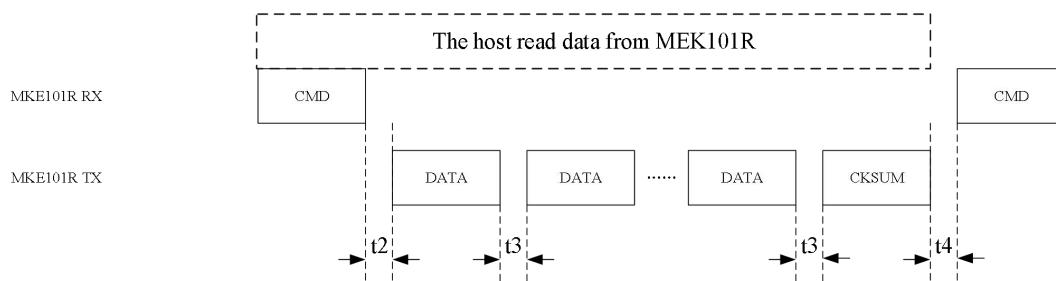

| 5.3 HSTX Interface .....                                 | 112 |

| 5.3.1 Overview of HSTX Interface .....                   | 112 |

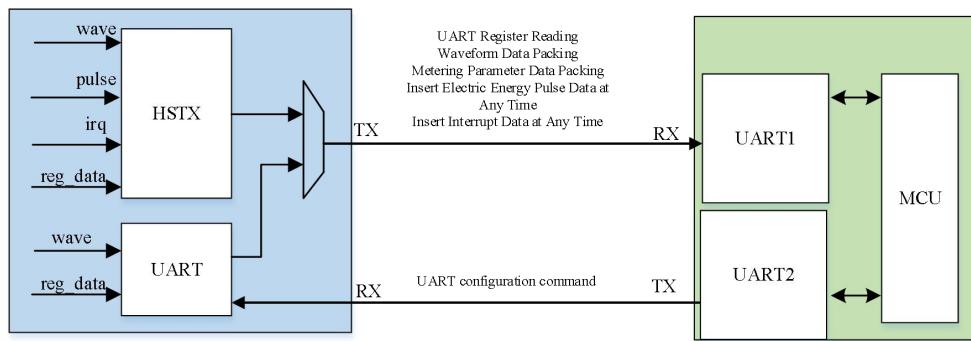

| 5.3.2 Features of HSTX Interface .....                   | 113 |

| 5.3.3 HSTX Data Format .....                             | 114 |

| 5.3.4 HSTX Frame Format .....                            | 120 |

| 5.3.5 HSTX Related Registers .....                       | 121 |

| 5.3.6 HSTX Application Process .....                     | 121 |

| 5.4 IIC Interface .....                                  | 122 |

| 5.4.1 Overview of IIC Interface .....                    | 122 |

| 5.4.2 Features of IIC Interface .....                    | 122 |

| 5.4.3 IIC Interface General Protocol .....               | 122 |

| 5.4.4 IIC Interface Specific Timing Specifications ..... | 123 |

| 5.4.5 IIC-related registers .....                        | 123 |

| 5.3.6 IIC Application Process .....                      | 123 |

| 6 Electrical Characteristics .....                       | 128 |

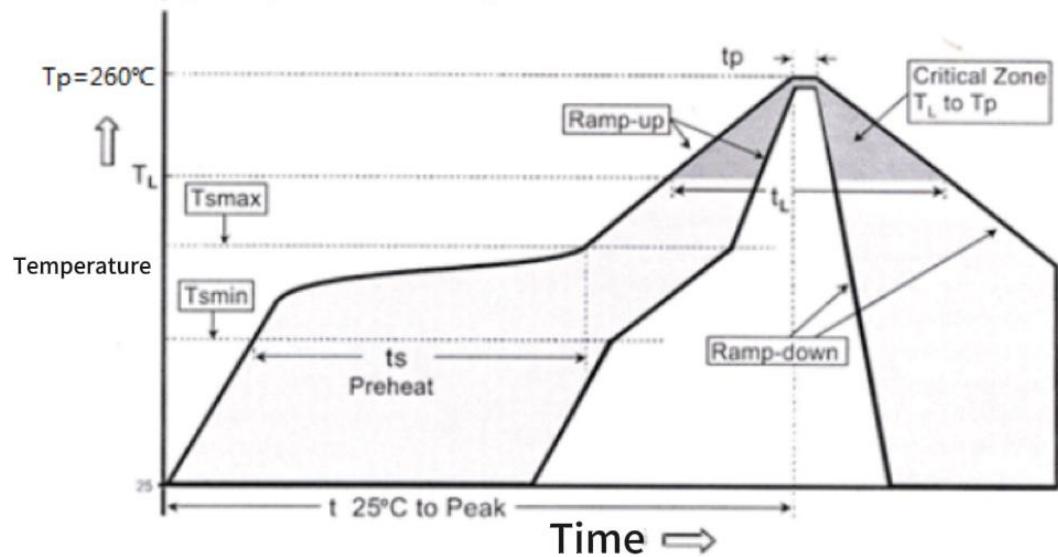

| 7 Chip Packaging and Soldering Conditions .....          | 133 |

| 9 Packaging Information .....                            | 135 |

## User Manual of Single-phase Metering Chip MKE101R Rev1.0

|                                                           |     |

|-----------------------------------------------------------|-----|

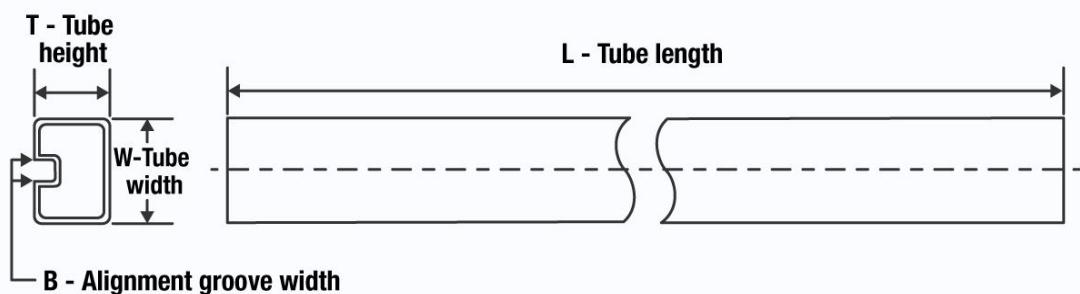

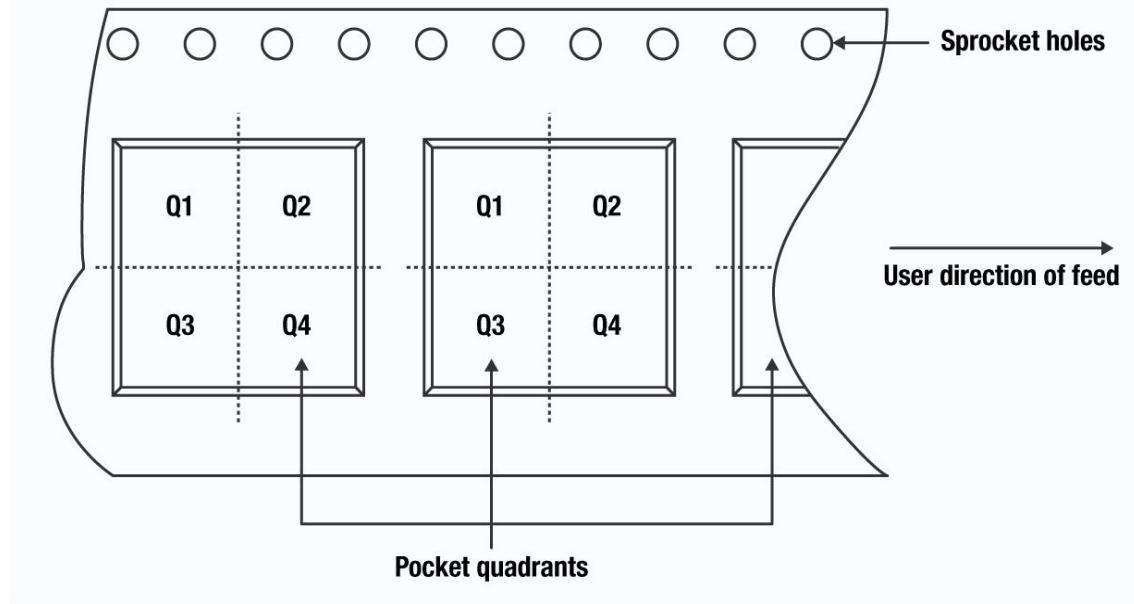

| 9.1 Material Pipe Specifications .....                    | 135 |

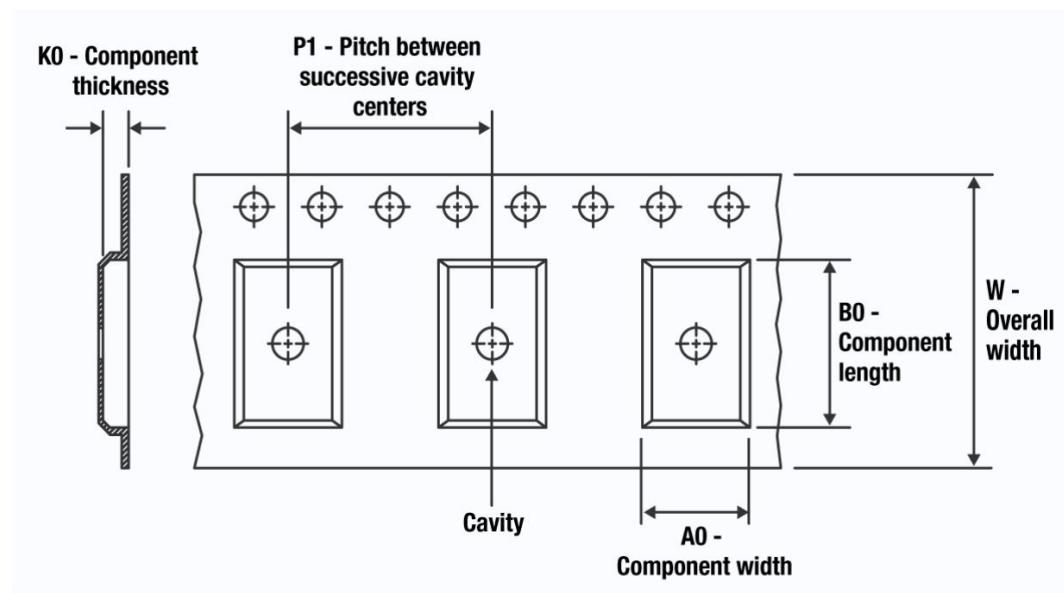

| 9.2 Tape Specifications .....                             | 136 |

| Appendix 1: Reactive Power Phase Compensation Table ..... | 138 |

# 1 Chip Introduction

The MKE101R, a high-precision and highly reliable single-phase metering chip by MAKSA, is designed for various metering applications including smart meters, energy consumption analysis, power monitoring, and electrical safety.

## 1.1 Chip Characteristics

- ✓ calculate

- It provides a three-channel sum-delta ADC, including the voltage channel (U channel), current channel A (IA channel), and current channel B (IB channel).<sup>①</sup>

- The IA channel PGA supports 4x,8x,12x,16x (default), 24x, and 32x amplification, but not 1x or 2x. The IB and U channel PGA support 1x,2x, and 4x amplification.<sup>②</sup>

- The active power metering performance of the front line (A line) shows a nonlinear error of <0.1% within a dynamic range of 20000:1.<sup>③</sup>

- The reactive power metering performance of the line maintains a non-linear error below 0.1% within a dynamic range of 20000:1.

- It provides three-channel RMS measurement. The IA channel has a dynamic range of 2000:1 with a nonlinearity error <0.1%. The IB and U channels have a dynamic range of 1000:1 with a nonlinearity error <0.1%.

- Provides two-phase active and reactive power output on the live and neutral lines (B channel), supporting dual-phase active and reactive power metering.

- A pulse frequency generator is provided for accumulating and integrating electrical energy at user-defined power levels.

- Provide three-channel ADC instantaneous sampling values and support instantaneous sampling value update interrupts

- The threshold for latent movement can be adjusted.

- It provides reverse active power indication and outputs the REVP reverse indication signal through the QF pin.

- Provide U-channel frequency measurement

- Provide U-channel zero-crossing detection

- Supports zero-crossing signals from Ia channels to be output through the TX pin of the UART port.

- Supports reference voltage monitoring, see VREF\_OK

- Supports bidirectional measurement to meet the requirements for rapid power flow change testing

- Active power supports both full-wave and fundamental wave metering.

- reactive power support fundamental wave metering

- Both active and reactive power support half-wave metering

- ✓ software calibration

- The meter constant (HFConst) is adjustable.

- Provide gain and phase correction

- Provide active, reactive, and RMS offset correction

- Provide small signal calibration acceleration function

- Enable automatic configuration parameter validation

- ✓ Supports arbitrary single-channel, dual-channel, or triple-channel ADC waveform buffering, with continuous waveform acquisition via SPI/UART ports.

- ✓ The RX input pin of a UART module serves dual functions: global reset (via the pin) and local reset (via the UART module).

- ✓ Features power monitoring capability

- ✓ Electric energy register with timing freeze function

- ✓ Supports synchronous sampling

- ✓ Supports fast leakage detection

- ✓ Supports DC detection

- ✓ Supports voltage and current transient event detection

- ✓ Supports single-phase three-wire  $\pm P_1 \pm P_2$  and  $\pm Q_1 \pm Q_2$  integration operations

- ✓ Configure register support for CRC16

- ✓ Supports adjustable pulse width and level inversion for power

- ✓ Supports  $I_a \pm I_b$  RMS calculation

- ✓ Supports asymmetric baud rate UART communication. The TX module features HSTX functionality with a baud rate of  $F_{osc}/4$  (crystal oscillator frequency). HSTS automatically transmits real-time waveforms, metering parameters, power pulses, interrupts, and other data. The RX baud rate and communication parameters remain unchanged.

- ✓ Supports IIC host communication for convenient interaction with external temperature sensor chips, used for terminal temperature measurement.

- ✓ Supports error self-monitoring function

- ✓ Supports software-adjustable UART baud rate

- ✓ The MKE101R operates on a +5V/3.3V power supply, with typical power consumption values of

| Crystal frequency<br>voltage | Power supply<br>5V | 3.3V  |

|------------------------------|--------------------|-------|

| 3.579545MHz                  | 27mW               | 15mW  |

| 5.5296MHz                    | 30 mW              | 16 mW |

- ✓ Built-in 1.25V $\pm 1\%$  reference voltage, with a typical temperature coefficient of 5ppm/ $^{\circ}\text{C}$  and a maximum of 15ppm/ $^{\circ}\text{C}$ .

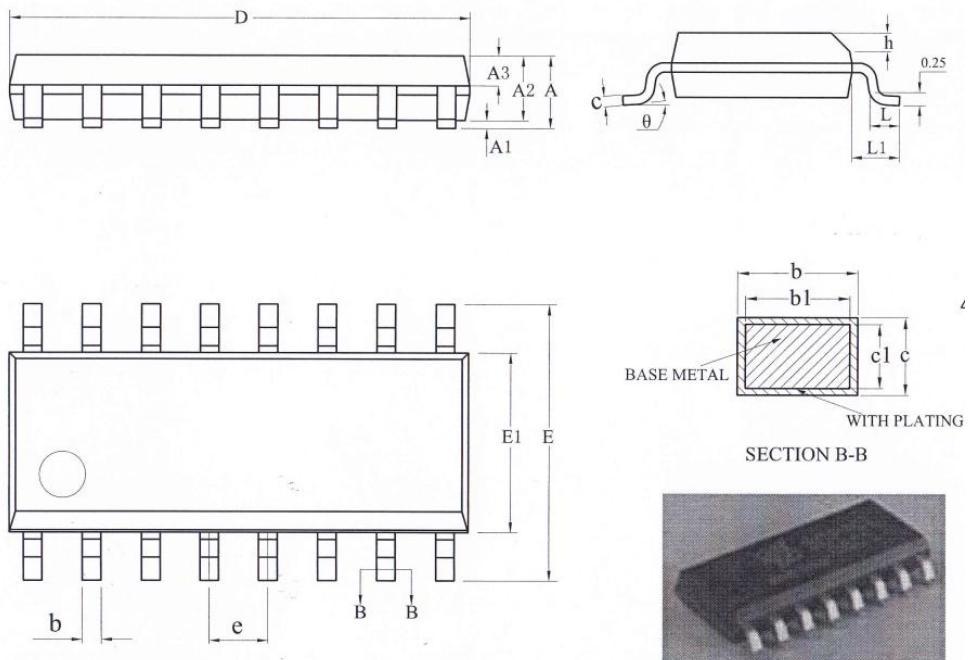

- ✓ The MKE101R is packaged in SOP16L green packaging.

- ①

- ②

- ③

Channel A is called IA channel, channel B is called IB channel, and channel U is called U channel.

In this article, red text indicates new or upgraded features in V5, which will not be repeated later.

The live wire is called A line, and the neutral wire is called B line.

## 1.2 Function Overview

The MKE101R meter provides comprehensive measurement capabilities for all-wave and fundamental wave active/reactive power, voltage/current RMS values, line frequency, and half-cycle updates of active/reactive power and voltage/current values. It supports dual independent channels for active/reactive power and current RMS values, with full compliance to all current metrology standards including active energy metering, reactive energy metering, fundamental wave metering,

half-wave metering, and bidirectional metering.

The MKE101R features fully digital gain, phase, and offset calibration. Active power pulses are output from the PF/QF/IRQ pins, while reactive power pulses, user-defined power pulses, and REV/P can be output from the same pins.

The MKE101R features both SPI and UART serial interfaces, enabling seamless communication with external microcontrollers.

The MKE101R features an IIC host interface for seamless communication with external temperature sensor chips, enabling terminal temperature measurement.

The MKE101R features an HSTX interface (high-speed UART TX interface) that automatically transmits real-time waveforms, measurement parameters, pulses, and other data.

The power monitoring circuit inside MKE101R can ensure the reliable operation of the chip when power is on and off.

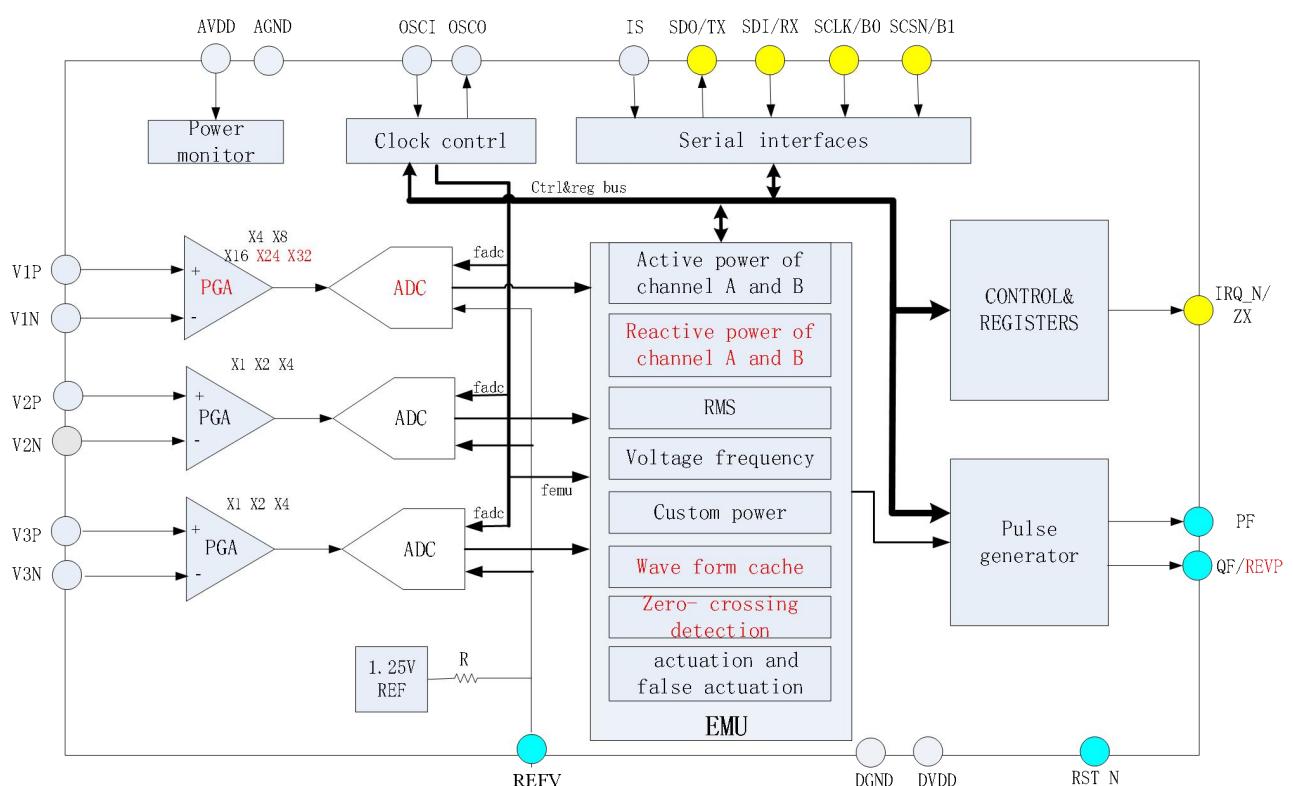

### 1.3 Function Block Diagram

Figure 1-1 Function Block Diagram

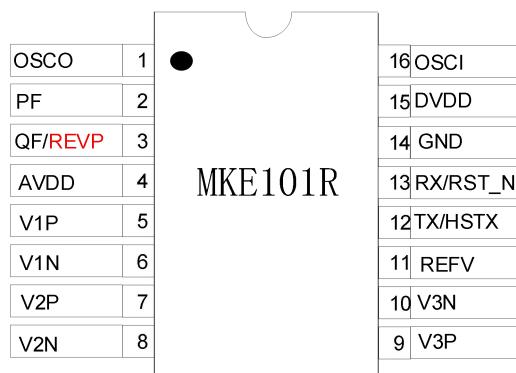

## 1.4 Pin Definitions

Figure 1-2 Pin layout diagram of MKE101R-SOP16L

| pin  | characteristic | characteristic | functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | OSCO           | output         | The output of the external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2    | PF             | output         | The active power pulse output defaults to low-level output. Its frequency reflects the instantaneous active power level. It has a 5mA output and current absorption capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3    | QF/ REVP       | output         | <p>This pin is a QF/REVP multiplex pin (default QF). When EMUCON2.QFCFG=0, it functions as a QF pin to output either reactive power verification pulses or user-defined pulses, with low-level output as the default. The frequency reflects the magnitude of either reactive power or user-defined power values, which include three options: second active power, sum of two active power vectors, or user-defined power register. It features a 5mA output and current absorption capability.</p> <p>When EMUCON2.QFCFG=1, the REVP pin functions as a negative power indicator.</p>                                                                                                              |

| 4    | AVDD           | source         | Analog power pin. This pin supplies power to the analog section of the chip. It should be externally connected with a 10 $\mu$ F capacitor in parallel and a 0.1 $\mu$ F decoupling capacitor. Typical operating voltage range: 2.97V to 5.5V. After selecting a standard supply voltage (e.g., 5V or 3.3V), ensure the power supply fluctuation remains within $\pm 10\%$ of the specified range.                                                                                                                                                                                                                                                                                                   |

| 5, 6 | V1P, V1N       | import         | <p>The positive and negative analog input pins of the I/O channel. It operates in full differential mode, with a maximum input voltage of <math>\pm 1000\text{mV}</math> and a maximum withstand voltage of <math>\pm 6\text{V}</math>.</p> <p>The external sampling circuit, when performing standard full-wave measurement, requires an anti-aliasing resistance of <math>1\text{k}\Omega</math> and an anti-aliasing capacitance ranging from <math>10\text{nF}</math> to <math>33\text{nF}</math>. For harmonic measurement or power quality analysis, the required anti-aliasing resistance is <math>1\text{k}\Omega</math> and the anti-aliasing capacitance is <math>3.3\text{nF}</math>.</p> |

|       |          |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 8  | V2P, V2N | import        | <p>The positive and negative analog input pins of the IB channel. It operates in full differential mode, with a maximum input V<sub>pp</sub> of <math>\pm 1000\text{mV}</math> and a maximum withstand voltage of <math>\pm 6\text{V}</math>.</p> <p><b>The external sampling circuit, when performing standard full-wave measurement, requires an anti-aliasing resistance of <math>1\text{k }\Omega</math> and an anti-aliasing capacitance ranging from <math>10\text{nF}</math> to <math>33\text{nF}</math>. For harmonic measurement or power quality analysis, the required anti-aliasing resistance is <math>1\text{k }\Omega</math> and the anti-aliasing capacitance is <math>3.3\text{nF}</math>.</b></p>                   |

| 9, 10 | V3P,V3N  | import        | <p>The U-channel features positive and negative analog input pins. It operates in fully differential mode, with a maximum input voltage of <math>\pm 1000\text{mV}</math> and a maximum withstand voltage of <math>\pm 6\text{V}</math> under normal operation.</p> <p><b>The external sampling circuit, when performing standard full-wave measurement, requires an anti-aliasing resistance of <math>1\text{k }\Omega</math> and an anti-aliasing capacitance ranging from <math>10\text{nF}</math> to <math>33\text{nF}</math>. For harmonic measurement or power quality analysis, the required anti-aliasing resistance is <math>1\text{k }\Omega</math> and the anti-aliasing capacitance is <math>3.3\text{nF}</math>.</b></p> |

| 11    | REFV     | Input/O utput | <p>The input/output pin for the <math>1.25\text{V}</math> reference voltage. The external reference source can be directly connected to this pin. Whether using an internal or external reference source, this pin should be decoupled with a minimum of <math>1\mu\text{F}</math> capacitor in parallel with a <math>0.1\mu\text{F}</math> capacitor.</p>                                                                                                                                                                                                                                                                                                                                                                            |

| 12    | TX       | output        | <p>This pin serves as the TX data output port for UART. Using special commands, it can generate a zero-crossing signal for the IA channel, typically a <math>10\text{ms}</math> square wave. For details, refer to the Special Commands section.</p> <p><b>The TX function can be reconfigured as HSTX. Operating at baud rates of Fosc/4 (<math>895\text{K}@3.579545\text{MHz}</math> or <math>1382\text{K}@5.5296\text{MHz}</math>), the TX pin automatically transmits real-time waveforms, measurement parameters, pulses, and other data.</b></p>                                                                                                                                                                                |

| 13    | RX/RST_N | import        | <p>This pin serves as both the UART input RX and a reset pin. A local reset (UART module reset) occurs when the low-level input signal persists for between <math>10\text{ms}</math> and <math>20\text{ms}</math>, while a global reset (chip-wide reset) is triggered if the signal remains low for over <math>20\text{ms}</math>.</p> <p>The internal reset circuit of MKE101R is completely independent of the UART communication circuit, and its pin reset function is identical to that of an independent pin reset.</p>                                                                                                                                                                                                        |

| 14    | GND      | the earth     | <p>In the chip circuit, ensure this pin is not directly connected to ground points with high digital noise (e.g., DVDD decoupling capacitor), and maintain a sufficient distance from them.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15    | DVDD     | source        | <p>Digital power pin. This pin supplies power to the digital section of the chip. It should be externally connected with a <math>10\mu\text{F}</math> capacitor in parallel and a <math>0.1\mu\text{F}</math> decoupling capacitor. Typical operating voltage range: <math>2.97\text{V}</math> to <math>5.5\text{V}</math>. After selecting a standard supply voltage (e.g.,</p>                                                                                                                                                                                                                                                                                                                                                      |

|    |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      |        | 5V or 3.3V), ensure the power supply fluctuation remains within $\pm 10\%$ of the specified range.                                                                                                                                                                                                                                                                                                                                                                                        |

| 16 | OSCI | import | The input terminal of the external crystal or the clock input of the external clock system. The typical frequency of the external crystal is 3.579545 MHz. The typical value of the external capacitor is 15 pF to 22 pF, and there is already an internal bypass resistance of approximately 4 M $\Omega$ , so no external bypass resistor is required. For 3.579545 MHz, the ESR of the external crystal must be less than 120 ohms; for 5.5296 MHz, the ESR must be less than 80 ohms. |

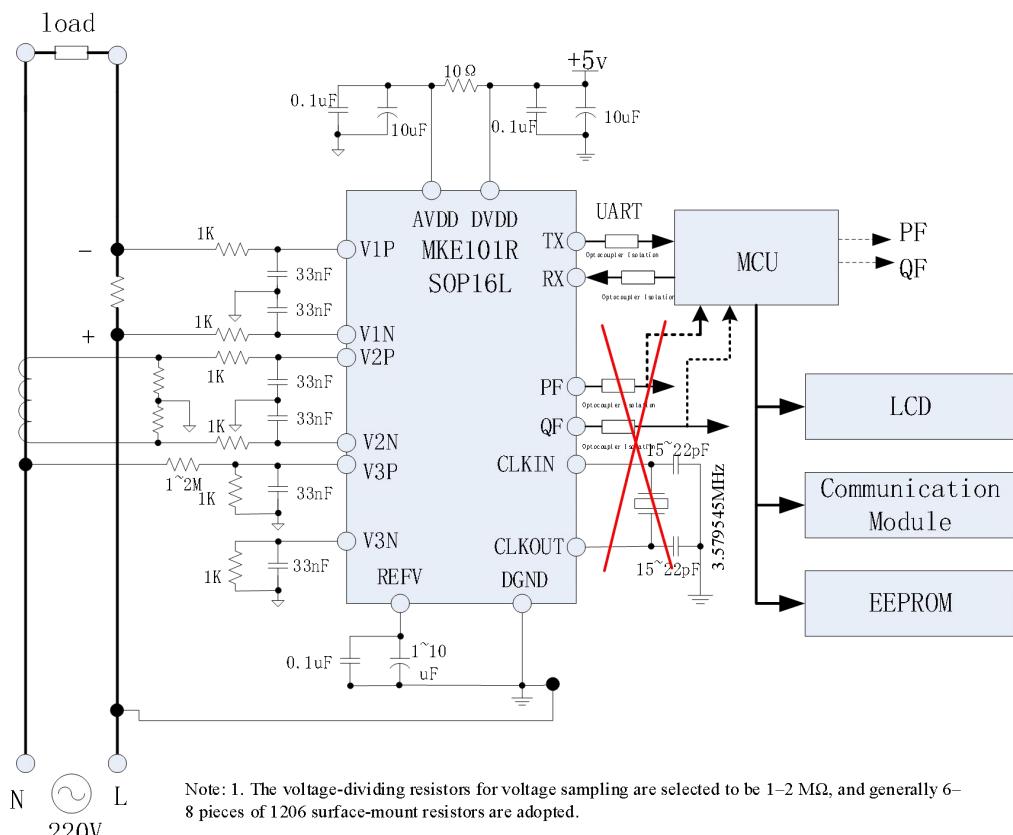

## 1.5 Typical Applications

### 1.5.1 State Grid Single-Phase 20 Version

Figure 1-5 Typical Applications of State Grid Single-phase Meters

The MKE101R features three  $\Sigma - \Delta$  ADC channels. The IA channel ADC (V1P/V1N inputs)

uses live-wire manganeseed copper for sampling, while the IB channel ADC (V2P/V2N inputs) employs neutral-wire transformer sampling. The U channel ADC (V3P/V3N inputs) handles voltage sampling. The high-performance IA channel ADC has a small manganeseed copper input signal and defaults to 16x PGA, whereas the IB and U channel ADCs have larger input signals and are configured at 1x PGA by default.

## 2 System Functions

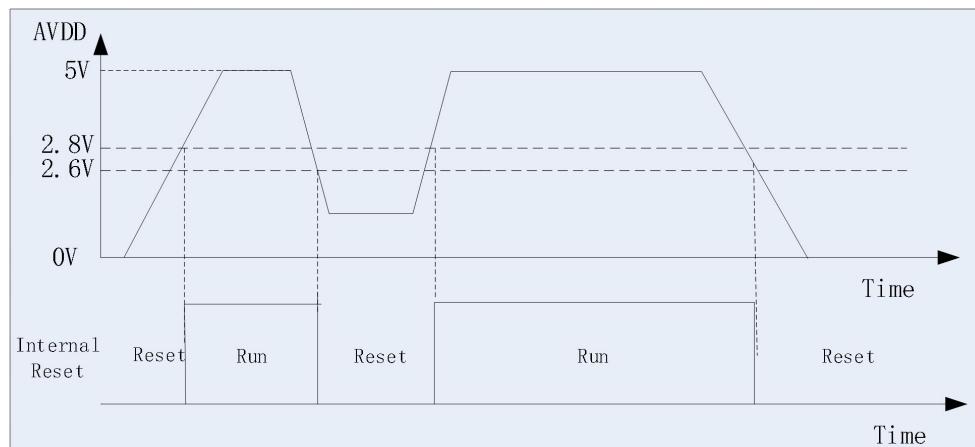

### 2.1 Power Monitoring

The MKE101R chip incorporates a power monitoring circuit that continuously tracks the analog power supply (AVDD). The chip resets when the voltage drops below  $2.6V \pm 0.1V$ , and operates normally when the voltage exceeds  $2.8V \pm 0.1V$ .

Figure 2-1 Power Supply Detection Characteristics

Normal operating range: 2.97V-5.5V. After selecting a typical supply voltage (e.g., 5.0V or 3.3V), ensure the power supply fluctuation remains within  $\pm 10\%$  of the specified range.

### 2.2 System Reset

The MKE101R supports three global reset modes:

- Up and down electricity

- External pin reset or RX pin reset

- command reset

The MKE101R supports a local reset mode:

- UART module reset

#### ➤global reset

When any global reset occurs, the register returns to its initial value, and the external pin levels revert to their original states.

The chip completes reset 15 microseconds after the reset command is issued.

The external reset pin of MKE101R first drops from high to low level and remains at low level for over 50 microseconds, then rises from low to high level for over 300 microseconds before releasing the reset.

The RX pin of the MKE101R also functions as a reset pin. When the input signal remains low for over 20ms at 3.579545MHz or 1.3 ms at 5.5296MHz, the metering chip recognizes this as a valid reset. This feature reduces the number of optocouplers required in isolated applications. The

internal reset circuit of the MKE101R is completely independent of the UART communication circuit, and its pin reset function is equivalent to that of an independent pin reset.

**The recommended RX pin reset procedure is: first set the RX pin low for 25ms at 3.579545MHz (F osc) and 17ms at 5.5296MHz (F osc), then set it high for 20ms, and finally initiate normal UART communication.**

#### ➤local reduction

The RX pin of MKE101R supports UART communication port reset functionality. When the input signal on the RX pin remains low for over 10ms at 3.579545MHz or 6.5ms at 5.5296MHz, the UART communication module of the metering chip will reset.

This function is recommended only when the MCU detects UART communication anomalies. For isolated UART interface reset, the RX pin should maintain low level for 15ms at 3.579545MHz Fosc and 10ms at 5.5296MHz Fosc. Note that exceeding 20ms at 3.579545MHz Fosc or 13ms at 5.5296MHz Fosc will trigger a full chip reset.

#### ➤Related registers:

The RST in the system status register is a hardware reset flag: it is set to 1 when the external RST\_N pin or power-up reset is completed, and cleared upon readout. This flag can be used for resetting and recalibrating data requests.

The SOFTRST in the system status register is a command reset flag: it is set to 1 when the command reset is completed and cleared after reading. This flag can be used for resetting and requesting calibration data.

It is suggested that the CPU should reset the metering chip by pin reset or command reset before initializing the metering chip.

## 2.3 Module Conversion

The MKE101R features three ADC channels: IA for live wire current sampling, IB for neutral wire current sampling, and U for voltage sampling. The SYSCON register (SYSCON 0x00H) with SYSCON[6] enables or disables the IB channel.

The ADC employs full-differential input, with the maximum signal input amplitude for current and voltage channels reaching 1000mVpp at peak.

By configuring SYSCON[5:0] in the SYSCON register and SYSCON2[1:0] in System Control Register 2 (SYSCON2 0x19H), the PGA of three ADC channels can be set individually. The IA channel PGA options are 4, 8, 12, 16 (default), 24, or 32; while the IB and U channel PGA options are 1 (default), 2, or 4.

## 2.4 Active Power

The MKE101R provides dual active power calculation and correction channels: A and B. The power update frequency is Fosc/2/2^19 (default), with 3.414Hz at Fosc 3.579545MHz and 5.27Hz at Fosc 5.5296MHz. Other update frequencies are configurable, as detailed in EMUCON2.UPMODE.

The register also contains two sets of registers for phase correction, active offset correction, active gain correction, and average power. The IB channel includes the gain correction register IBGain, which affects the active power of the B channel and the IB RMS value.

The current average active power (PowerP) channel for detecting latent motion and activation,

along with the instantaneous active power channel (DATAP) for calculating active energy, are selected between channels A and B based on specific commands, as detailed in the Special Commands section.

The user can configure the channel selection through special commands, and the configuration results can be queried via the CHNSEL register bit.

The digital high-pass filter in Figure 2-2 is mainly used to remove the DC component in the current and voltage sampling data.

In Figure 2-2, DCIA, DCIB, and DCU are used to correct the DC bias of the ADC channel. When the MKE101R is used for DC measurement applications, it is necessary to correct the DC bias and disable the high-pass filter.

## 2.5 Reactive Power

The MKE101R features dual reactive power and reactive energy calculation circuits for PowerQ/PowerQB and dual reactive energy. The power update frequency is set to  $F_{osc}/2/2^{19}$  (default), with  $3.414Hz@F_{osc}3.579545MHz$  and  $5.27Hz@F_{osc} 5.5296MHz$ . Other update frequencies are configurable, as detailed in EMUCON2.UPMODE.

The MKE101R features dual-channel fundamental reactive power and electrical energy calculation. As the fundamental reactive power function cannot support two channels simultaneously, it defaults to outputting A-channel fundamental reactive power. A dedicated command allows switching to B-channel fundamental reactive power output.

## 2.6 Effective Value

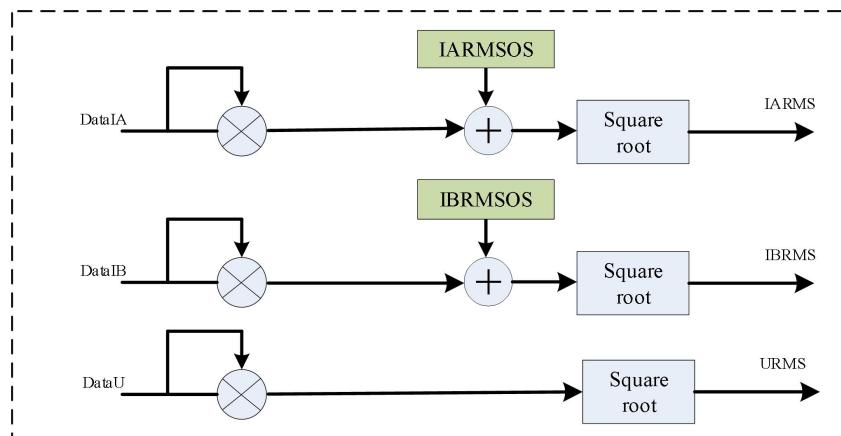

Figure 2-4 Effective Value Calculation Block Diagram

The MKE101R provides three-channel true RMS output parameters: URMS, IARMS, and IBRMS. With a 24-bit word length, it supports true RMS updates at three frequencies: 3.414Hz at 3.579545MHz  $F_{osc}$  (default), 5.27Hz at 5.5296MHz  $F_{osc}$ , and customizable frequencies as specified in EMUCON2.UPMODE. The device also includes two true RMS offset registers: IARMSOS and IBRMSOS.

Channel 2 gain correction (IBGain) affects the output of IBRMS, while other phase corrections, power gain corrections, and power offset corrections do not affect the RMS calculation results.

## 2.7 Energy Calculation

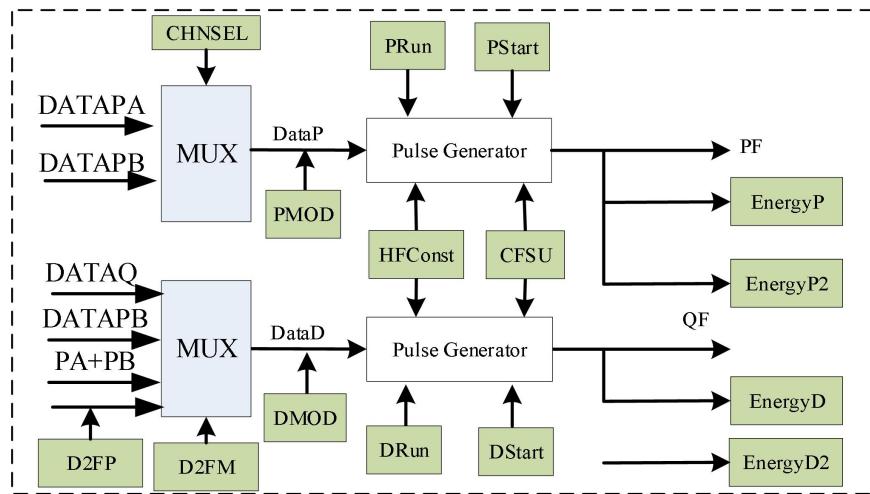

Figure 2-5 Energy Calculation

### Energy pulse output:

THE PULSE OUTPUT, ALSO KNOWN AS CALIBRATION PULSE OUTPUT, CAN BE DIRECTLY CONNECTED TO A STANDARD ELECTRICITY METER FOR ERROR COMPARISON.

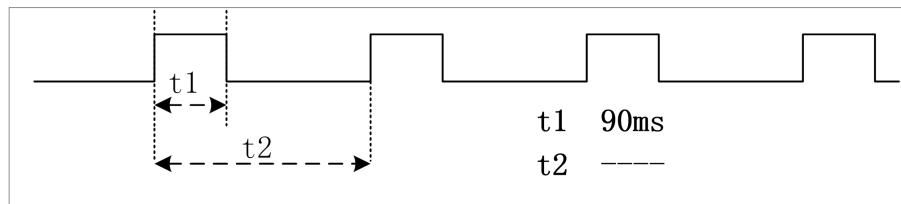

THE PF/QF OUTPUT MUST SATISFY THE FOLLOWING TIMING RELATIONSHIP:

Figure 2-6 Output Pulse Width

**Note:** When the pulse output period is less than 180ms, the pulse is output in equal duty form.

### Relationship between PFcnt/DFcnt, HFConst, pulse output, and energy register:

When  $2*|PFcnt|$  (0x20H) equals HFConst (0x02H), the PF generates a pulse output. Simultaneously, the energy registers EnergyP (0x29H) and EnergyP2 (0x2AH) are incremented by 1.

When  $2*|DFcnt|$  (0x21H) equals HFConst (0x02H), the QF generates a pulse output. Simultaneously, the energy registers EnergyD (0x2BH) and EnergyD2 (0x2CH) are incremented by 1.

### Relationship between pulse output, energy register, and PRun/DRun and PStart/DStart:

The active / custom energy register and PF / QF output are also controlled by PRun / DRUN and PStart / DStart.

- When PRun equals zero or  $|P|$  is less than PStart, the PF does not generate pulses, and neither PFcnt nor the functional quantity register increments.

- When DRUN equals zero or  $|DataD|$  is less than DStart, the QF does not generate pulses, and neither DFcnt nor the custom energy register increments.

### Custom pulse output:

DataDs default source is DATAQ (reactive power), but users can select DATAPB (second active power channel), DATAPA+DATAPB (two-channel power vector sum), or D2FP (user-defined) through the D2FM register to specify the power source.

#### **Pulse output acceleration:**

To accelerate small-signal correction, the system provides pulse output acceleration capability. During correction, the CFSUEN and CFSU[1:0] bits of the EMUCON (0x01H) register can be configured to boost the output frequency of PF/QF, achieving up to 16-fold enhancement.

#### **Reverse direction:**

When the active or custom power is negative, the REVP or REVQ bit in the EMUStatus register is set to 1. The REVP bit updates in sync with the PF pulse, while the REVQ bit updates in sync with the QF pulse.

## **2.8 Channel Switching**

The MKE101R features a dedicated ADC channel for zero-line current RMS and power measurement, with A/B channel switching capability to enable users to select specific current channels for active power measurement.

Channel switching is implemented via special command words (see Special Command Registers section). The configuration results can be queried through the CHNSEL register bit.

## **2.9 Frequency Measurement**

The MKE101R directly outputs line frequency parameters (UFreq 0x25H) to measure fundamental frequency. Its minimum measurement frequency is 6.8Hz at 3.579545MHz frequency, and 4.4Hz at 5.5296MHz frequency, with a measurement bandwidth of 250Hz.

The MKE101R also features an additional line frequency parameter register (UFreq2 0x35) for measuring fundamental frequency, with a minimum measurement frequency of 1Hz at 3.579545MHz and 0.65Hz at 5.5296MHz, and a measurement bandwidth of 250Hz.

## **2.10 Start-up of the Submerged Motor**

The start threshold is configured by the PStart and DStart registers. These 16-bit unsigned numbers are compared with the absolute values of the high 24 bits of PowerP and DataD (32-bit signed numbers) to determine the start condition.

When PowerP is less than PStart, PF does not output pulses.

When DataD is less than DStart, QF does not output pulses.

The default reset value for PStart is 0x0060H, and for DStart, it is 0x0120H.

When the power is below the startup power, the NoPlD bit in the EMUStatus register is set to 1; when the active power reaches or exceeds the startup power, the NoPlD bit is cleared to 0.

When DataD is below the startup power, NoPlD is set to 1; when the custom power reaches or exceeds the startup power, NoPlD is reset to 0.

## 2.11 Event Detection

The MKE101R enables/disables zero-crossing output via the ZXCFG (EMUCON.7) configuration, using the IRQ\_N/ZX pin.

The MKE101R supports four zero-crossing output modes by configuring the ZXD1 (EMUCON.9) and ZXD0 (EMUCON.8) register bits.

The MKE101R supports the UART TX pin to output an IA zero-crossing signal. In UART communication mode, a special command can be set to enable the TX pin to output an IA zero-crossing signal, typically a 10ms square wave. If the channel special command or the UART RX pin remains low for over 10ms, the UART module will reset and disable the zero-crossing output function, reverting to the TX function of the UART communication port. For details, refer to the special commands section.

The MKE101R supports voltage and current event detection, including voltage drop, overload in current channel A, overload in current channel B, and overload in voltage channel.

The event threshold register includes: voltage drop threshold register USAG, current channel A peak detection threshold register, current channel B peak detection threshold register, voltage channel peak detection threshold register.

The voltage drop threshold register is a 16-bit unsigned number. This function remains disabled when the value is zero. Upon writing a non-zero value, voltage drop detection is activated. The threshold is compared with the high 16 bits of the 24-bit waveform sampling value from channel 24, with the detection half-period count determined by SYSCON2.USAG\_CFG[7:0]. If the voltage drop duration exceeds the USAG\_CFG threshold, a voltage drop event is triggered, and the detection result is reported as an interrupt.

The peak detection threshold register is a 16-bit unsigned number. This function remains disabled when the value is zero. Upon writing a non-zero value, the drop detection is activated. The threshold is compared with the high 16 bits of the 24-bit waveform sampling value from channel 24, which is sampled synchronously with the current. If the waveform sampling value exceeds the threshold, an overload event is triggered, and the detection result is reported via an interrupt.

Note: The 24-bit waveform sampling value of the synchronous sampling channel is approximately  $0.5*Vin*2^{23}$ , where Vin is the normalized input signal value, and the normalized value is 1 when the amplitude is 1V.

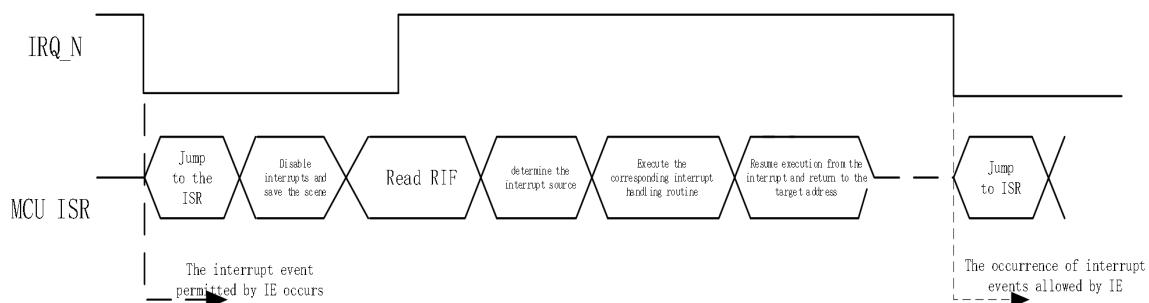

## 2.12 Interruption

The MKE101R interrupt resources comprise: 1 interrupt enable register (IE), 2 interrupt status registers (IF and RIF), and a multiplexed interrupt request pin (IRQ\_N/ZX). The RIF and IF registers function in tandem-reading RIF clears IF, and vice versa.

The MKE101R waveform buffer interrupt resources comprise two registers: WAVE\_IE (waveform buffer interrupt enable) and WAVE\_IF (waveform buffer status). Writing to the WAVE\_IF flag clears both the flag and the associated interrupt.

### 1. Interrupt request signal IRQ\_N

The IRQ\_N/ZX pin serves as a multiplexed signal combining IRQ\_N and zero-crossing detection output ZX. Its function is determined by configuring the ZXCFG bit in the EMUCON register (0x01H).

When the interrupt enable bit in the interrupt enable register is set and an interrupt occurs, the IRQ\_N pin remains low. The pin returns to high when the CPU reads RIF or IF via the SPI interface, following the SCLK falling edge of the last bit (LSB) in the command byte.

## 2. Interrupt Handling Process

### hardware :

- The IRQ\_N pin of MKE101R is typically connected to the MCUs external interrupt pin (INT). When IRQ\_N transitions from high to low, the MCU generates an INT interrupt.

- The MCU acts as the host for SPI or UART, while the MKE101R functions as the slave for SPI or UART.

### interrupt handler :

#### Step 1: MCU Interrupt Initialization

1. The MCU reads the MKE101R RIF and clears the interrupt flags for IF and RIF;

2. Configure the MKE101R IE register to enable the required interrupt enable bit for generating IRQ\_N;

3. Enable the MCUs INT external interrupt, wait for the MKE101R interrupt event to occur, then the IRQ\_N output triggers the INT interrupt, jumping to the INT interrupt entry address.

#### Step 2: Interrupt Service Routine in MCU

1. Disable the MCUs global interrupt and INT interrupt;

2. The MCU reads the RIF register via SPI, clears both the IF and RIF registers, and sets IRQ\_N back to high level.

3. The MCU determines the interrupt source of MKE101R by checking the RIF interrupt flag, then executes the corresponding interrupt handler.

4. After executing the interrupt handler, the MCU activates both global and INT interrupts, then returns to the original state.

After returning from an interrupt, if the /INT interrupt flag is detected, the program re-enters the external interrupt service routine (ISR) and repeats step 2. If the /INT interrupt flag is not detected, it indicates no interrupt event occurred during the interrupt handling process, and the program continues to run.

Figure 2-7 MKE101R interrupt handling process

## 2.13 Waveform Buffer

The MKE101R features a built-in  $256 \times 20$ -bit SRAM waveform buffer module that stores ADC sampling waveforms for FFT analysis and power quality evaluation.

The waveform buffer source supports three options: full-wave data (Fosc/2/128 sampling rate), fundamental wave data (Fosc/2/128 sampling rate), and synchronous sampling data (determined by synchronization configuration). It also allows buffering of any single, dual, or triple-channel waveform data from the IA/IB/U channels.

Users can access the cache content through various read commands. The read pointer increments by 1 for each accessed point. When the address exceeds the cache length, it resets to the starting address.

Users can change the read pointer position using special commands (configure the waveform pointer address). The read pointer automatically resets to the starting address each time the waveform buffer is started.

### 2.13.1 Characteristics of Waveform Buffer

- The waveform buffer has a maximum size of 256×20, with a depth of 256 addresses. Each buffer contains 20 bits of waveform data.

- The waveform buffer can be configured to use either full-wave measurement data, fundamental wave measurement data, or synchronized sampling channels as the data source.

- Supports continuous and single cache

- You can cache I1/I2/U three-channel waveform data. Each data source can be configured as single-channel, dual-channel, or three-channel cache. The three-channel cache stores 64 points per channel.

- In multi-channel caching, two caching modes can be selected: channel contiguous caching and channel cross caching.

- Configure interval caching to double or quadruple the interval

- Waveform data can be read out through three interfaces: SPI, UART, and HSTX. When reading data, you can select either 24-bit or 16-bit waveform data, and different channels can be independently selected.

- Waveform data output supports high byte first/low byte first

- The read pointer automatically returns to the first address each time the waveform buffer is initialized.

- Continuous buffering uses ping-pong operation to cache and output real-time waveforms.

- The software can read the busy flag or obtain the waveform buffer status through interrupts.

- When the cache reaches half full, the half-block SRAM waveform data can be read out via the SPI or HSTX interfaces.

- Software-readable busy flag or data overwrite interrupt, retrieve waveform buffer status

### 2.13.2 Waveform Buffering Method

#### **data cache speed**

The waveform buffers capacity and half-full time are shown in the table below, with 256-point waveforms loaded each time.

| number of channels | intermediate buffer configue | SRAM size (dots) | Cache half-full time (ms) | Cache full time (ms) |

|--------------------|------------------------------|------------------|---------------------------|----------------------|

| 1                  | 4x buffer                    | 256              | 40                        | 80                   |

| 2                  | 4x buffer                    | 256              | 20                        | 40                   |

| 3                  | 4x buffer                    | 192              | 10                        | 20                   |

| 1                  | double buffer                | 256              | 20                        | 40                   |

| 2                  | double buffer                | 256              | 10                        | 20                   |

| 3                  | double buffer                | 192              | 5                         | 10                   |

| 1                  | Cache all                    | 256              | 10                        | 20                   |

| 2                  | Cache all                    | 256              | 5                         | 10                   |

| 3                  | Cache all                    | 192              | 2.5                       | 5                    |

Since the length of the waveform data in the cache is 20 bits, which is not a multiple of 8, it is not convenient to frame the received data. Therefore, the chip usually processes the waveform data to 24 bits or 16 bits when sending.

### Data output speed

The waveform data is processed for 16-bit transmission, with its data volume and transmission time analyzed as shown in the table below. The HSTX transmission speed is  $F_{osc}/4$ , specifically 894.886 kHz at  $F_{osc}$  3.579545 MHz and 1382.4 kHz at  $F_{osc}$  5.5296 MHz. As HSTX employs the UART protocol, each 8-bit data requires 11 bits of transmission. Thus, the actual HSTX transmission speed is calculated as  $F_{osc}/4/11 \times 8$ , yielding 650826 at  $F_{osc}$  3.579545 MHz.

| number of channels | intermediate buffer configue | bit width of transmission | semi-fulfilling point | Half-full data volume (bits) | Half-full interrupt time (ms) | SPI velocity | SPI half-full data transmission time (ms) | HSTX Speed @ $F_{osc}$ 3.579545 MHz | HSTX half-full data transmission time (ms) |

|--------------------|------------------------------|---------------------------|-----------------------|------------------------------|-------------------------------|--------------|-------------------------------------------|-------------------------------------|--------------------------------------------|

| 1                  | 4x buffer                    | 16                        | 128                   | 2048                         | 40                            | 1200000      | 1.71                                      | 650826                              | 3.15                                       |

| 2                  | 4x buffer                    | 16                        | 128                   | 2048                         | 20                            | 1200000      | 1.71                                      | 650826                              | 3.15                                       |

| 3                  | 4x buffer                    | 16                        | 96                    | 1536                         | 10                            | 1200000      | 1.28                                      | 650826                              | 2.36                                       |

| 1                  | double buffer                | 16                        | 128                   | 2048                         | 20                            | 1200000      | 1.71                                      | 650826                              | 3.15                                       |

| 2                  | double buffer                | 16                        | 128                   | 2048                         | 10                            | 1200000      | 1.71                                      | 650826                              | 3.15                                       |

| 3                  | double buffer                | 16                        | 96                    | 1536                         | 5                             | 1200000      | 1.28                                      | 650826                              | 2.36                                       |

| 1                  | Cache all                    | 16                        | 128                   | 2048                         | 10                            | 1200000      | 1.71                                      | 650826                              | 3.15                                       |

|   |           |    |     |      |     |         |      |        |      |

|---|-----------|----|-----|------|-----|---------|------|--------|------|

| 2 | Cache all | 16 | 128 | 2048 | 5   | 1200000 | 1.71 | 650826 | 3.15 |

| 3 | Cache all | 16 | 96  | 1536 | 2.5 | 1200000 | 1.28 | 650826 | 2.36 |

The waveform data is processed into 16-bit transmission, with its data volume and transmission time analyzed as shown in the table below:

| number of channels | intermediate buffer configuration | bit width of transmission | semi -fulfilling point | Half-full data volume (bits) | Half-full interrupt time (ms) | SPI velocity | SPI half-full data transmission time (ms) | HSTX Speed @Fosc 3.5795 45MHz | HSTX half-full data transmission time (ms) |

|--------------------|-----------------------------------|---------------------------|------------------------|------------------------------|-------------------------------|--------------|-------------------------------------------|-------------------------------|--------------------------------------------|

| 1                  | 4x buffer                         | 24                        | 128                    | 3072                         | 40                            | 12000 00     | 2.56                                      | 650826                        | 4.72                                       |

| 2                  | 4x buffer                         | 24                        | 128                    | 3072                         | 20                            | 12000 00     | 2.56                                      | 650826                        | 4.72                                       |

| 3                  | 4x buffer                         | 24                        | 96                     | 2304                         | 10                            | 12000 00     | 1.92                                      | 650826                        | 3.54                                       |

| 1                  | double buffer                     | 24                        | 128                    | 3072                         | 20                            | 12000 00     | 2.56                                      | 650826                        | 4.72                                       |

| 2                  | double buffer                     | 24                        | 128                    | 3072                         | 10                            | 12000 00     | 2.56                                      | 650826                        | 4.72                                       |

| 3                  | double buffer                     | 24                        | 96                     | 2304                         | 5                             | 12000 00     | 1.92                                      | 650826                        | 3.54                                       |

| 1                  | Cache all                         | 24                        | 128                    | 3072                         | 10                            | 12000 00     | 2.56                                      | 650826                        | 4.72                                       |

| 2                  | Cache all                         | 24                        | 128                    | 3072                         | 5                             | 12000 00     | 2.56                                      | 650826                        | 4.72                                       |

| 3                  | Cache all                         | 24                        | 96                     | 2304                         | 2.5                           | 12000 00     | 1.92                                      | 650826                        | 3.54                                       |

The table above shows that when using the three-channel maximum speed buffer, the HSTX interface cannot achieve real-time waveform output for ping-pong operations with a 24-bit waveform length.

When using the waveform data of two channels (current and voltage) with the current channel transmitting 24-bit and the voltage channel transmitting 16-bit (the standard configuration for HSTX interface), the data transmission volume and time analysis are shown in the table below:

| number of channels | Wave frequency (Hz) | semi -fulfilling point | Half-full data volume (bits) | Half-full interrupt time (ms) | SPI velocity | SPI half-full data transmission time (ms) | HSTX Speed @Fosc 3.579545 MHz | HSTX half-full data transmission time (ms) |

|--------------------|---------------------|------------------------|------------------------------|-------------------------------|--------------|-------------------------------------------|-------------------------------|--------------------------------------------|

|                    |                     |                        |                              |                               |              |                                           |                               |                                            |

|   |               |     |      |    |          |      |        |      |

|---|---------------|-----|------|----|----------|------|--------|------|

| 2 | 4x buffer     | 128 | 2560 | 20 | 12000 00 | 2.13 | 650826 | 3.93 |

| 2 | double buffer | 128 | 2560 | 10 | 12000 00 | 2.13 | 650826 | 3.93 |

| 2 | Cache all     | 128 | 2560 | 5  | 12000 00 | 2.13 | 650826 | 3.93 |

The analysis above demonstrates that, regardless of the caching mechanism or transmission method employed, both SPI and HSTX can deliver real-time waveform outputs for ping-pong operations.

### 2.13.3 Cache Address Mapping

#### single channel cache

| address mapping | BANK  | WAVECON[3:0], WAVECON[4]=X |     |     |  |  |  |

|-----------------|-------|----------------------------|-----|-----|--|--|--|

|                 |       | 0x2                        | 0x3 | 0x1 |  |  |  |

| 00H             | BANK0 | IA                         | IB  | UA  |  |  |  |

| 3FH             |       |                            |     |     |  |  |  |

| 40H             |       |                            |     |     |  |  |  |

| 7FH             |       |                            |     |     |  |  |  |

| 80H             | BANK1 |                            |     |     |  |  |  |

| BFH             |       |                            |     |     |  |  |  |

| C0H             |       |                            |     |     |  |  |  |

| FFH             |       |                            |     |     |  |  |  |

#### dual channel cache

##### channel gap buffer

| address mapping | BANK  | WAVECON[3:0], WAVECON[4]=1 |     |     |

|-----------------|-------|----------------------------|-----|-----|

|                 |       | 0x6                        | 0x7 | 0x8 |

| 00H             | BANK0 | IA                         | IA  | IB  |

| 3FH             |       | UA                         | IB  | UA  |

| 40H             |       | IA                         | IA  | IB  |

| 7FH             |       | UA                         | IB  | UA  |

| 80H             | BANK1 | IA                         | IA  | IB  |

| BFH             |       | UA                         | IB  | UA  |

| C0H             |       | IA                         | IA  | IB  |

| FFH             |       | UA                         | IB  | UA  |

##### channel crossing buffer

| address mapping | BANK  | WAVECON[3:0], WAVECON[4]=0 |      |      |

|-----------------|-------|----------------------------|------|------|

|                 |       | 0x6                        | 0x7  | 0x8  |

| 00H             | BANK0 | IA0                        | IA0  | IB0  |

| 01H             |       | UA0                        | IB0  | UA0  |

| ...             |       | ...                        | ...  | ...  |

| 7EH             |       | IA63                       | IA63 | IB63 |

|     |       |       |       |       |

|-----|-------|-------|-------|-------|

| 7FH |       | UA63  | IB63  | UA63  |

| 80H | BANK1 | IA64  | IA64  | IB64  |

| 81H |       | UA64  | IB64  | UA64  |

| ... |       | ...   | ...   | ...   |

| FEH |       | IA127 | IA127 | IB127 |

| FFH |       | UA127 | IB127 | UA127 |

The table above shows the channel cross-cache address mapping, where IAn denotes the n-th acquisition data from the IA channel, IBn from the IB channel, and UAn from the UA channel.

### three channel buffer

channel gap buffer

| address mapping | BANK  | WAVECON[3:0], WAVECON[4]=1 |

|-----------------|-------|----------------------------|

|                 |       | 0xD                        |

| 00H             | BANK0 | IA                         |

| ...             |       |                            |

| 1FH             |       | IB                         |

| 20H             |       |                            |

| ...             |       | UA                         |

| 3FH             |       |                            |

| 40H             |       | IA                         |

| ...             |       |                            |

| 5FH             | BANK1 | IB                         |

| 60H             |       |                            |

| ...             |       | UA                         |

| 7FH             |       |                            |

| 80H             |       | IA                         |

| ...             |       |                            |

| 9FH             |       | IB                         |

| A0H             |       |                            |

| ...             | BANK1 | UA                         |

| BFH             |       |                            |

| ...             |       |                            |

| FFH             |       |                            |

channel crossing buffer

| address mapping | BANK  | WAVECON[3:0], WAVECON[4]=0 |

|-----------------|-------|----------------------------|

|                 |       | 0xD                        |

| 00H             | BANK0 | IA0                        |

| 01H             |       | IB0                        |

| 02H             |       | UA0                        |

| ...             |       | ...                        |

| 5CH             |       | IA31                       |

| 5EH             |       | IB31                       |

| 5FH             |       | UA31                       |

|     |       |      |

|-----|-------|------|

| 60H | BANK1 | IA32 |

| 61H |       | IB32 |

| 62H |       | UA32 |

| ... |       | ...  |

| BCH |       | IA63 |

| BEH |       | IB63 |

| BFH |       | UA63 |

| ... |       |      |

| FFH |       |      |

#### 2.13.4 Cache and Read Commands

#### waveform buffer start stop command

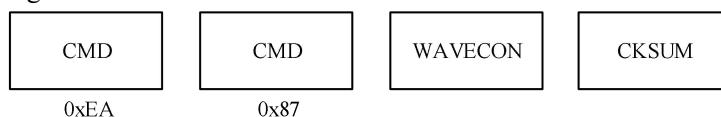

The host initiates the waveform buffer operation by transmitting a special command byte (2 bytes) followed by channel selection (1 byte) and read checksum (1 byte). Upon receiving this command, the MKE101R activates or deactivates the buffer according to WAVECOM configuration, as illustrated in the diagram below.

Figure 2-11 Start and Stop Command Frame Format

The command word WAVECON in the waveform buffer command is defined as follows:

- WAVECON[7]: Set to 0 to enable waveform buffering, or 1 to disable it. When 1 is set, the value of WAVECON[6:0] is ignored.

- WAVECON[6]: =0 for single buffer (stop after storage); =1 for continuous buffer.

- WAVECON[5]: Reserved

- WAVECON[4]: Cache mode selection. Valid only with dual-channel cache. =0: Select channel cross cache; =1: Select channel interleaved cache.

- WAVECON[3:0]: Cache channel and cache sequence selection. The corresponding cache channels and sequences are shown in the table below:

| WAVECON[3:0] | Cache channels and order (cache order from left to right) |    |   |   |

|--------------|-----------------------------------------------------------|----|---|---|

| 0 x 0        | Do not start cache                                        |    |   |   |

| 0 x 1        | UA                                                        | -  | - | - |

| 0 x 2        | IA                                                        | -  | - | - |

| 0 x 3        | IB                                                        | -  | - | - |

| 0 x 4        | UA                                                        | IA | - | - |

| 0 x 5        | UA                                                        | IB | - | - |

| 0 x 6        | IA                                                        | UA | - | - |

| 0 x 7        | IA                                                        | IB | - | - |

| 0 x 8        | IB                                                        | UA | - | - |

|       |    |    |    |

|-------|----|----|----|

| 0 x 9 | IB | IA | -  |

| 0 x A | UA | IA | IB |

| 0 x B | UA | IB | IA |

| 0 x C | IA | UA | IB |

| 0 x D | IA | IB | UA |

| 0 x E | IB | IA | UA |

| 0 x F | IB | UA | IA |

matters need attention :

- 1、Before writing the startup command, the clock gate control for the ADC waveform buffer must be enabled via the clock control register CLKCON.

- 2、When the waveform buffer is active, the host initiates the command, the read is invalid, returns data 0, and the read pointer remains unchanged.

- 3、To switch between single or continuous waveform buffering, stop the buffering first.

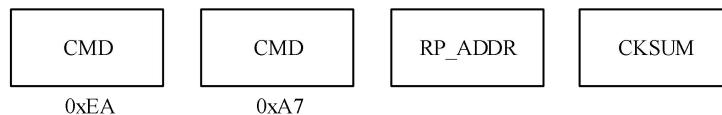

### Read waveform buffer pointer address configuration command

The host initiates the configuration of the read waveform pointer address by sending a special command byte (2 bytes) followed by the pointer address (1 byte) and the checksum byte (1 byte). Upon receiving this command, the MKE101R sets the read buffer pointer address to RP\_ADDR, as illustrated in the diagram below.

Figure 2-12 Command Frame Format for Pointer Address Configuration

After the read pointer address is configured, if the host initiates a single read of waveform data, the slave will return the corresponding cache address data. Upon completion of the read, the pointer automatically increments by 1, where RP\_ADDR is the read pointer address of the SRAM.

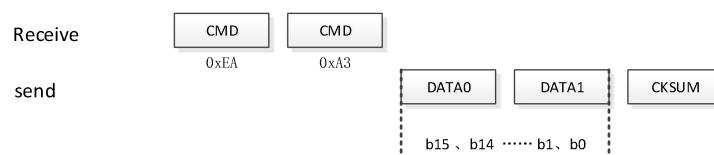

### single read waveform command

The host initiates a single read operation by first transmitting a special command byte (2 bytes). Upon receiving this command, the MKE101R transmits a read data byte (2 bytes) and a read checksum byte (1 byte), as illustrated in the figure below.

Figure 2-13 Single Read Waveform Command Frame Format

matters need attention :

- 1、After each waveform reading, the corresponding read pointer increments by 1. When the last address is read, the read pointer resets to the starting position.

## continuous read waveform command

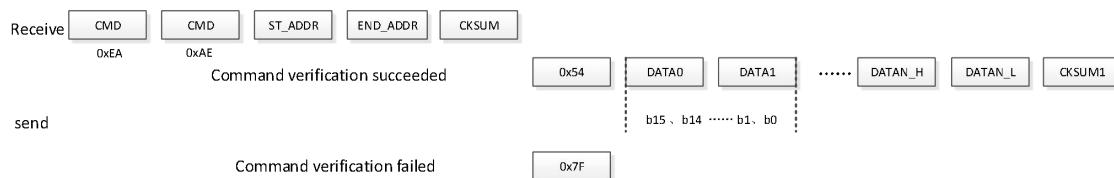

The continuous read operation is initiated by the host, which first transmits a special command byte (2 bytes) followed by the start address (1 byte), end address (1 byte), and checksum (1 byte).

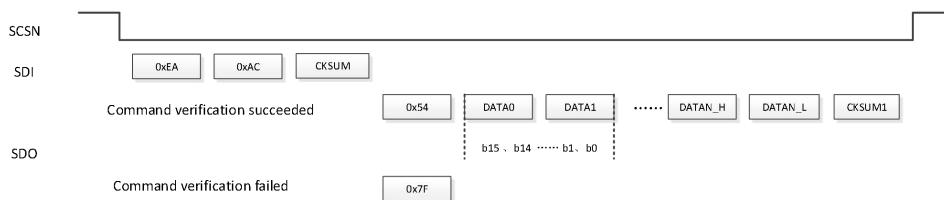

The MKE101R determines whether the command check passes. If passed, it returns a successful command receipt (0x54), then transmits the read data byte (nByte), and finally sends the read checksum byte. If the command check fails, it returns a failed command receipt (0x7F) and stops transmitting subsequent data. As shown in the figure below:

Figure 2-14 Continuous Read Waveform Command Frame Format

matters need attention :

- 1、The host sends a checksum CHKSUM (CHKSUM =  $\sim(0xE4+0xAE+ST\_ADDR+END\_ADDR)$ ) after the command. The slave checks the checksum to confirm command reception. If successful, it sends an ACK (0x54) response, then transmits the read data (length determined by ST\_ADDR and END\_ADDR), and finally sends the second checksum CHKSUM1.

- 2、CHKSUM 1 (CHKSUM1 =  $\sim(DATA0+...+DATAn)$ ) excludes ACK from its verification scope, focusing solely on waveform data validation.

- 3、If the slave detects a checksum error in the masters command, it returns an ACK (0x7F) indicating failure and terminates the command.

- 4、When the address exceeds the boundary, the transmission is deemed failed, and the failure flag 0x7F is returned.

- 5、The slave computer calculates and sends the data frame checksum, and the host computer determines whether the data frame transmission is successful based on the checksum.

- 6、ST\_ADDR and END\_ADDR must be within the range of 0 to 155, with END\_ADDR being greater than or equal to ST\_ADDR.

- 7、After the command is successfully executed, the read pointer stops at END\_ADDR+1.

## half bit read wave command

The half-read waveform command is only valid in SPI communication mode. After the host activates SCSN, it first writes a special command byte (2 bytes) via SPI, followed by the checksum (1 byte). Upon receiving the read command, the slave device outputs data bit by bit from the SDO pin during the rising edge of SCLK, as shown in the figure below.

Figure 2-15 Half-read waveform command frame format

matters need attention :

1. The host sends a command followed by an 8-bit checksum (CHKSUM). The slave checks the CHKSUM to verify command transmission success. If successful, it returns the success flag 0x54, then transmits waveform data and the checksum. If verification fails, it returns the failure flag 0x7F.

2. After successful machine calibration, the system continuously outputs 78 consecutive waveform data points. Each data point read increments the read pointer by 1. Assuming the read pointer address is RP\_ADDR before command initiation, the system reads waveforms from RP\_ADDR to (RP\_ADDR+77) after command execution, with the pointer settling at (RP\_ADDR+78) upon command completion. A loop design ensures that if the pointer exceeds the boundary 0x9B, it resets to 0x00 and resumes reading.

3. After transmitting the waveform of the specified length, an 8-bit checksum is immediately sent. The checksum does not include the ACK, but only verifies the waveform data.

4. For every 16-bit waveform data, transmit the high bits first, then the low bits.

### 2.13.5 Waveform Buffer Application Description

#### ●SPI Communication Waveform Buffer Application:

- 1、During configuration, the clock control register CLKCON activates the ADC waveform buffer clock gating.

- 2、Configure waveform buffer half full interrupt and data overwrite error interrupt;

- 3、Configure WAVECOMs caching mode, such as U/IA dual-channel continuous waveform caching, and enable waveform caching.

- 4、When the waveform buffer reaches half full, a half-full interrupt is generated, and the MCU triggers an INT interrupt as IRQ\_N transitions from high to low.

- 5、The MCU reads the WAVE\_HF\_IF register via SPI, clears it, and sets IRQ\_N back to high level.

- 6、**The MCU reads continuous waveform data in either continuous or half-block mode using special commands (recommended SPI\_SCLK frequency should be no less than 600kHz).**

- 7、**The MCU processes data according to the waveform buffer format to obtain complete waveforms for both U and IA channels.**

- 8、**The MCU performs power quality analysis through complete continuous waveforms, including FFT, abrupt rises and falls, flicker, and other characteristics.**

- 9、The WAVECOM[7] module in WAVECOM can disable waveform buffering.

#### ●UART communication waveform buffer application:

- 1、During configuration, the clock control register CLKCON activates the ADC waveform

buffer clock gating.

- 2、Configure WAVECOMs caching mode: for IA channels, enable single-channel waveform caching (UART interface supports only single-channel caching), and activate waveform caching.

- 3、When the buffer reaches full capacity (refer to the buffer schedule), the waveform buffering will automatically stop.

- 4、The MCU configures the pointer address of the read buffer through special commands and reads the waveform data in either single or consecutive modes.

- 5、The user can analyze the waveform of the output half-wave or full-wave data.

●HSTX communication waveform buffer application:

be continued

## 2.14 Checksum and CRC (Cyclic Redundancy Check)

### 2.14.1 Scope of Validation

| address                                             | name    | R/<br>W | wor<br>d<br>len<br>gth | Reset value | checksu<br>m range  | CRC<br>check<br>range | CRC check<br>sequence |

|-----------------------------------------------------|---------|---------|------------------------|-------------|---------------------|-----------------------|-----------------------|

| <b>meter register and metering control register</b> |         |         |                        |             | <b>MKE10<br/>1R</b> | <b>MKE10<br/>1R</b>   | <b>MKE101R</b>        |

| 00H                                                 | SYSCON  | R/W     | 2                      | 0003h       | √                   | √                     | 1                     |

| 01H                                                 | EMUCON  | R/W     | 2                      | 0003h       | √                   | √                     | 2                     |

| 02H                                                 | HFConst | R/W     | 2                      | 1000h       | √                   | √                     | 3                     |

| 03H                                                 | PStart  | R/W     | 2                      | 0060h       | √                   | √                     | 4                     |

| 04H                                                 | DStart  | R/W     | 2                      | 0120h       | √                   | √                     | 5                     |

| 05H                                                 | GPQA    | R/W     | 2                      | 0000h       | √                   | √                     | 6                     |

| 06H                                                 | GPQB    | R/W     | 2                      | 0000h       | √                   | √                     | 7                     |

| 07H                                                 | PhsA    | R/W     | 1                      | 00h         | √                   | √                     | 8                     |

| 08H                                                 | PhsB    | R/W     | 1                      | 00h         | √                   | √                     | 9                     |

| 09H                                                 | QPhsCal | R/W     | 2                      | 0000h       | √                   | √                     | 10                    |

| 0AH                                                 | APOSA   | R/W     | 2                      | 0000h       | √                   | √                     | 11                    |

| 0BH                                                 | APOSB   | R/W     | 2                      | 0000h       | √                   | √                     | 12                    |

| 0CH                                                 | RPOSA   | R/W     | 2                      | 0000h       | √                   | √                     | 13                    |

| 0DH                                                 | RPOSB   | R/W     | 2                      | 0000h       | √                   | √                     | 14                    |

| 0EH                                                 | IARMSOS | R/W     | 2                      | 0000h       | √                   | √                     | 15                    |

| 0FH                                                 | IBRMSOS | R/W     | 2                      | 0000h       | √                   | √                     | 16                    |

| 10H                                                 | IBGain  | R/W     | 2                      | 0000h       | √                   | √                     | 17                    |

| 13H                                                 | DCIAH   | R/W     | 2                      | 0000h       | √                   | √                     | 18                    |

| 14H                                                 | DCIBH   | R/W     | 2                      | 0000h       | √                   | √                     | 19                    |

| 15H                                                 | DCUH    | R/W     | 2                      | 0000h       | √                   | √                     | 20                    |

|                                                       |             |     |   |           |   |   |                                             |

|-------------------------------------------------------|-------------|-----|---|-----------|---|---|---------------------------------------------|

| 16H                                                   | DCL         | R/W | 2 | 0000h     | ✓ | ✓ | 21                                          |

| 17H                                                   | EMUCON2     | R/W | 2 | 0000h     | ✓ | ✓ | 22                                          |

| 18H                                                   | QPhsCal 2   | R/W | 2 | 0000h     | ✓ | ✓ | 23                                          |

| 19H                                                   | SYSCON2     | R/W | 2 | 0000h     | ✓ | ✓ | 24                                          |

| 1AH                                                   | CLKCON      | R/W | 2 | 0000h     | ✓ | ✓ | 25                                          |

| 1BH                                                   | HFCConst2   | R/W | 2 | 0000h     | ✓ | ✓ | 26                                          |

| 1CH                                                   | HFCConst3   | R/W | 2 | 0000h     | ✓ | ✓ | 27                                          |

| 5EH                                                   | GFS         | R/W | 2 | 0000h     | ✓ | ✓ | 28                                          |

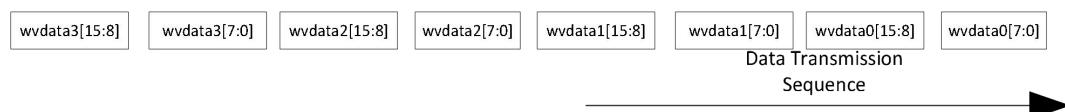

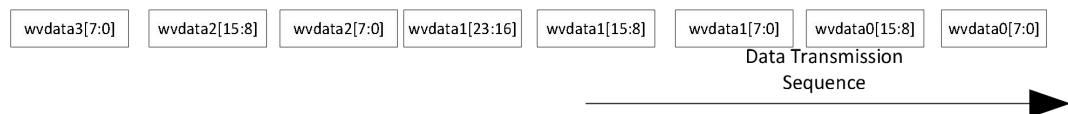

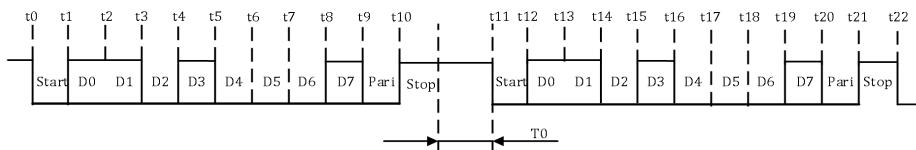

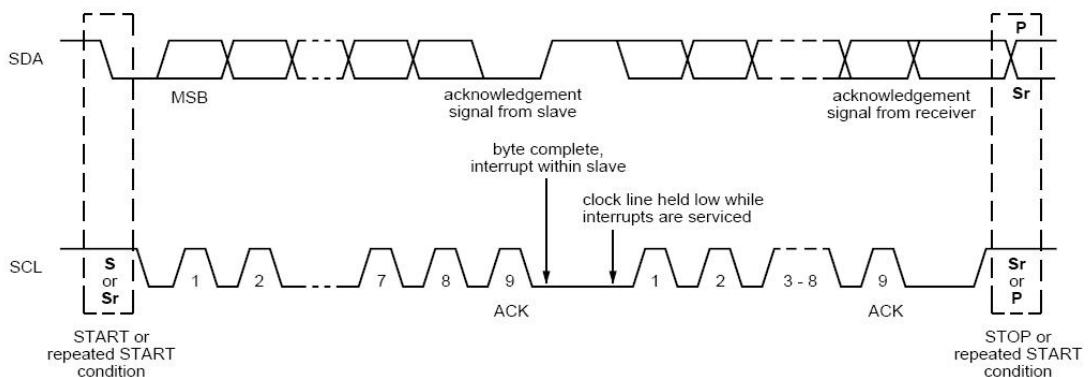

| 60H                                                   | EMUCON3     | R/W | 2 | 0000h     | ✓ | ✓ | 29                                          |